# Development Status of EUV Mask Blank and Substrate

# Asahi Glass Co. Ltd. Masaki Mikami

- 1. Introduction

- 2. Blank defect reduction

- 3. Integrated performance of ML Blank

- 4. Process development

- 5. Summary and future plan

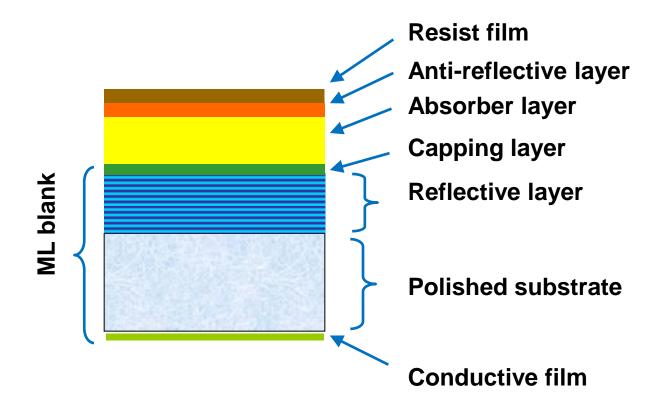

## 1-1. Structure of AGC EUVL blank

■ EUVL mask blank has a stack of reflective, capping, absorber and antireflective layers on its front side for a patterning and a conductive layer on its back side for mask chucking.

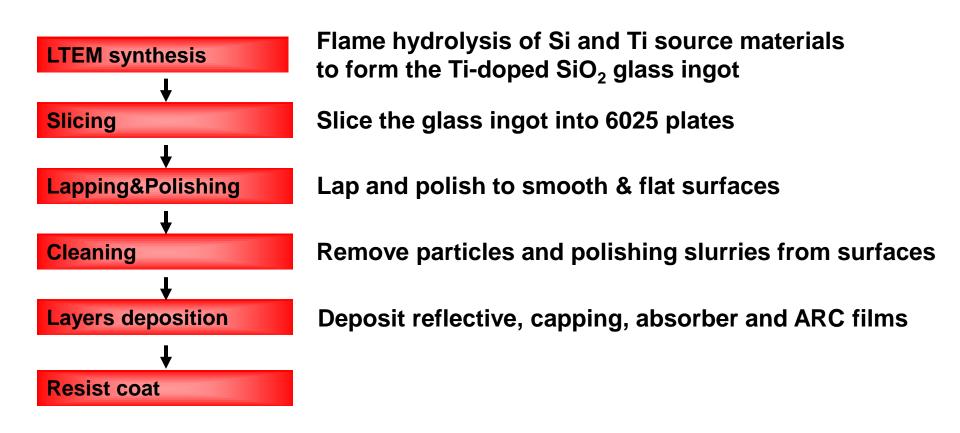

# 1-2. EUVL blank manufacturing process

■ AGC is the only supplier to take care of all essential processes and materials to EUV mask blank, starting from <u>LTEM</u> to film materials.

# 1-3. Required properties for EUVL blank

- Here is the list of major properties required for EUVL blank.

AGC has in-house metrology toolset to evaluate all of these properties.

- Defect data of substrate and ML will be mainly updated.

| Polished substrate               | Thermal expansion coefficient Surface flatness Surface roughness Surface local slope Surface defect (particle and pit)                      |  |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Reflective layer & Capping layer | Surface & Embedded defect (particle) EUV & DUV optical properties Film stress (blank bow) Durability to dry etch and wet cleaning chemicals |  |  |

| Absorber & Antireflective layer  | Surface & Embedded defect (particle) EUV & DUV optical properties Film stress Dry Etch capability Durability to wet cleaning chemicals      |  |  |

- 1. Introduction

- 2. Blank defect reduction

- 3. Integrated performance of ML Blank

- 4. Process development

- 5. Summary and future plan

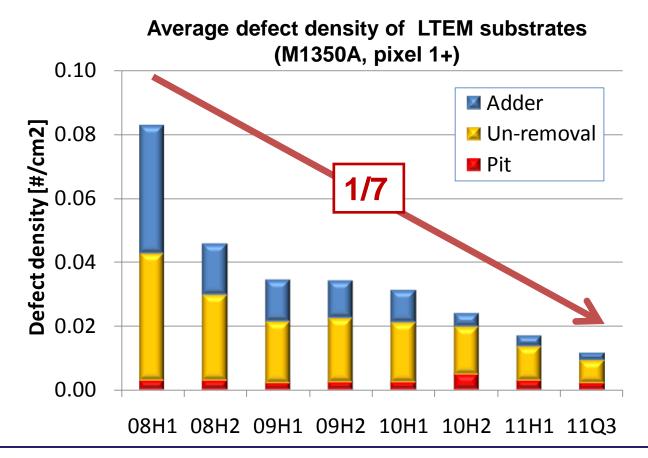

## 2-1. LTEM substrate defect trend

- This is the trend of the average defect density of LTEM substrate.

- We are optimizing polishing and cleaning processes to reduce "Pit", "Adder particle" and "Un-removal particle"

- Defect density has been reduced continuously.

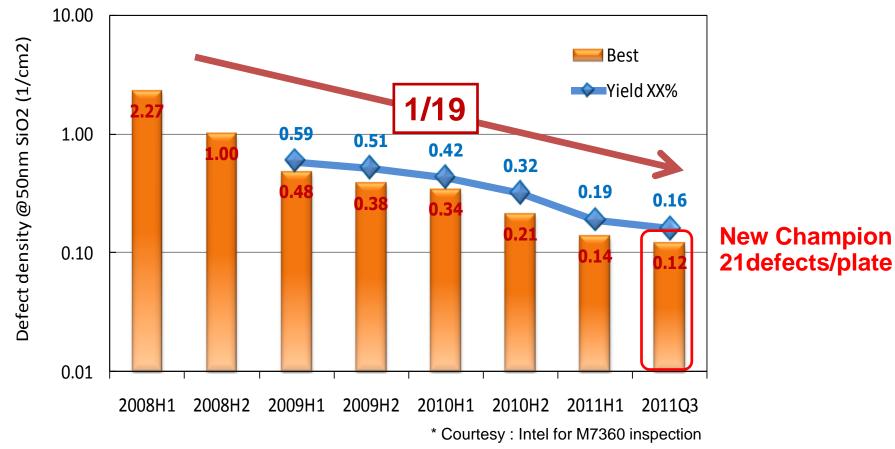

## 2-2. LTEM-ML blank defect trend @50nm SiO2

■ This is the updated defect trend of the LTEM-ML blank (LTEM substrate flatness <150nm). "NEW CHAMPION" defect density is 0.12/cm2 (21defects/plate) at 50nm SiO2 w/M7360. The defect density at yield XX% has also been continuously decreased.

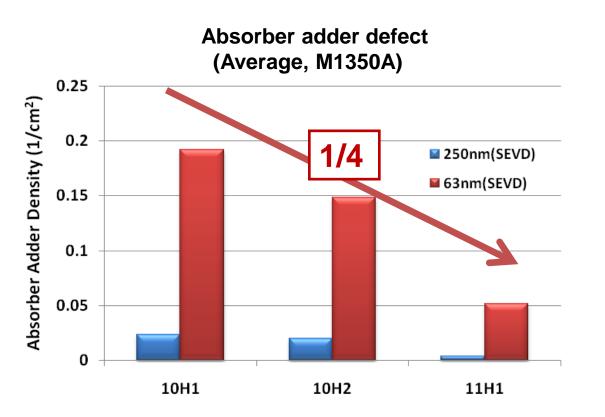

## 2-3. Absorber and ARC defect trend

- AGC has also been working on absorber and ARC defect reduction.

- The adder defect count has been decreased by optimizing coating equipment and deposition conditions.

The current best added defect density of absorber is 0 @ 63 nm SEVD in 132 x 132 mm.

"CHAMPION"

Adder defect map & Histogram

(M1350A,132x132mm)

- 1. Introduction

- 2. Blank defect reduction

- 3. Integrated performance of ML Blank

- 4. Process development

- 5. Summary and future plan

# 3. Integrated performance of LTEM-Full blank

■ The ML defect champion blank satisfied other properties. This blank also had low absorber defect count.

#### **Absorber**

Flatness (Front/Back)

Blank w/TaN&TaON

< 600nm / < 600nm

4 adder defects (0.023 defect/cm²) @63nm SEVD

### **EUV Reflectivity**

Peak %R 63.2 % R range (Abs.) 0.3 % Centroid  $\lambda$  (to target) -0.002 nm

28 defects (0.17 defect/cm²) @50nm SiO2 (~30nm SEVD)

ML

$\lambda \ range$

0.014 nm

**LTEM**

**CTE of LTEM**

Mean CTE 1.9 ppb/K

CTE variation (PV) 4.5 ppb/K

Flatness (Front/Back)

Substrate 89/75 nm

- 1. Introduction

- 2. Blank defect reduction

- 3. Integrated performance of ML Blank

- 4. Process development

- 5. Summary and future plan

# 4-1. Modified substrate material (LTEM)

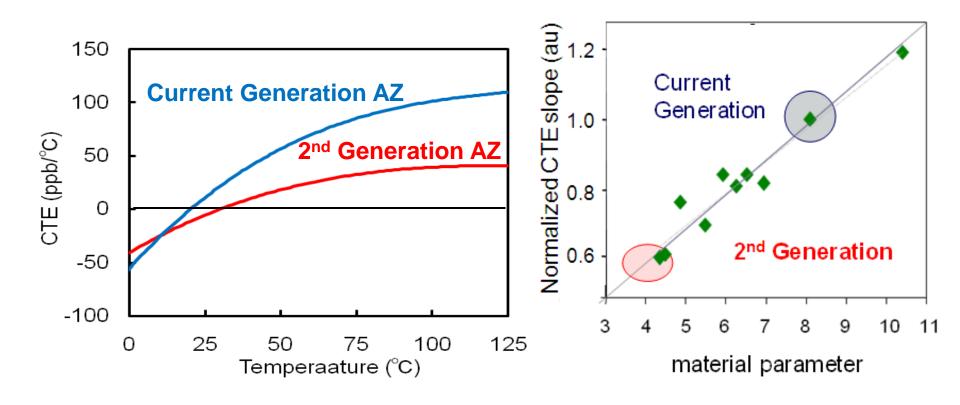

- AGC has been developing the modified LTEM (2<sup>nd</sup> Generation AZ) which showed lower CTE slope than the current LTEM.

- We have developed to control CTE slope with a material parameter. Slope is possible to be reduced 1.6 times than current level.

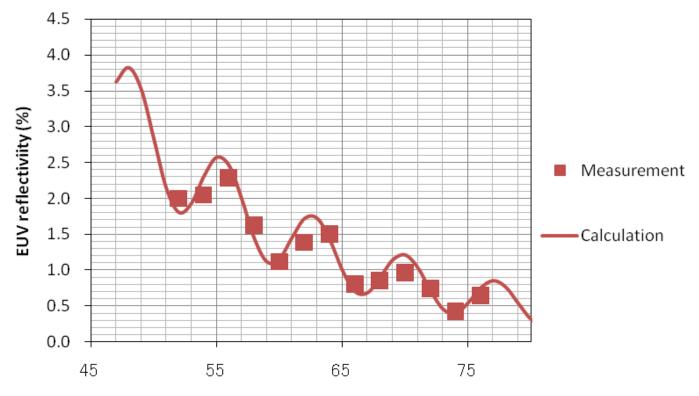

# 4-2. EUV reflectivity on absorber and ARC

- This figure shows EUV reflectivity dependency on the absorber and ARC thickness. Because of EUV light multiple reflection and its interference, it's dependency shows oscillation.

- AGC can adjust the absorber and ARC thickness to give the local minimum of the EUV reflectivity by using the in-house EUV reflectometer.

Total Thickness of absorber and ARC (nm)

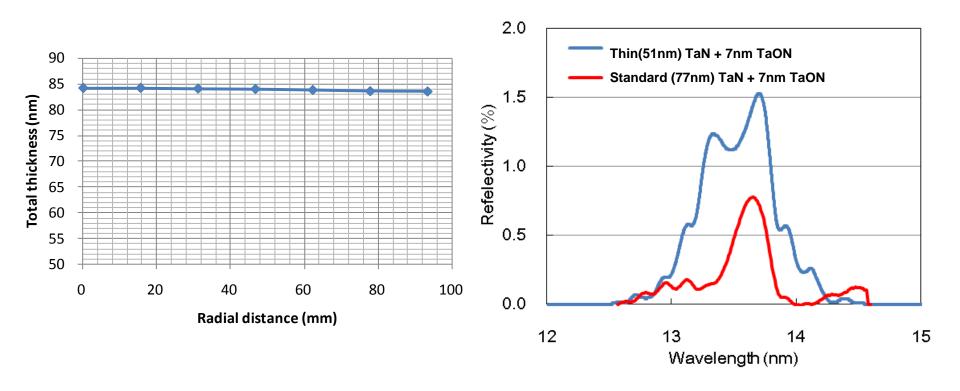

# 4-3. Absorber uniformity & EUV reflectivity

- AGC's absorber has the uniformity of 0.8% (0.7nm) range in total absorber/AR thickness, as shown in left figure. Its measurement accuracy is 0.2% (0.1nm).

- AGC has two kinds of absorber thickness. 77nm and 51nm, whose EUV reflectivity spectrum are shown below.

## 4-4. EUV blank for PPT

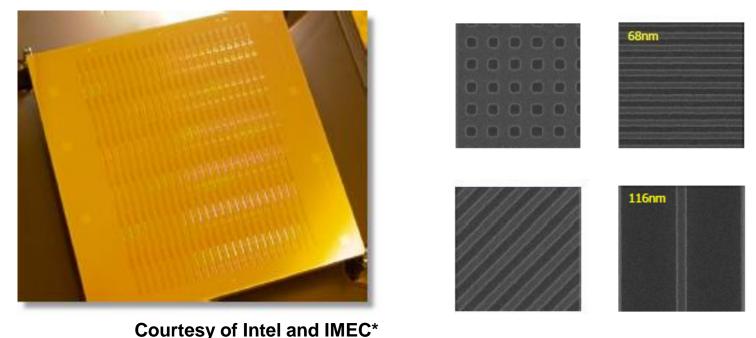

AGC blanks have been widely used to fabricate EUV reticles for PPT exposure tools in EUVL pilot lines. AGC has provided 1<sup>st</sup> generation EUVL blanks suitable for use in an EUV mask pilot line supporting PPT exposure tools.

#### **EUVL** mask photograph

<sup>\*</sup> Guojing Zhang, et al., "EUV mask readiness for high volume manufacturing", International Symposium on EUVL (2010)

- 1. Introduction

- 2. Blank defect reduction

- 3. Integrated performance of ML Blank

- 4. Process development

- 5. Summary and future plan

# 5. Summary and future plan

- AGC can provide 1<sup>st</sup> generation EUVL blanks suitable for EUVL pilot lines with PPT exposure tools.

- The ML blank defect and its inspection are remaining technical issues for HVM. AGC has been optimizing the EUVL blank fabrication processes to reduce the defect. The current best defect performance is 0.12/cm2 at 50nm SiO2 w/M7360.

- AGC is also developing 2<sup>nd</sup> generation blank including the material developments such as the modified LTEM, the new capping film material, and the thin absorber material.

|                            | 2010                         | 2011 | 2012 | 2013 | 2014 |

|----------------------------|------------------------------|------|------|------|------|

| 1 <sup>st</sup> generation | Process development          |      |      | HVM  |      |

| 2 <sup>nd</sup> generation | Process & material developme |      |      | nent | HVM  |

# **Acknowledgements**

Intel for all M7360 inspection.

Thank you for your attention.