# Development of EUV mask substrates with low thermal expansion

Yuuki Shiota, Shouji Shimojima, Morio Hosoya, Mitusharu Tsukahara\*, Takeyuki Yamada\*, Kesahiro Koike\* and Tsutomu Shoki\*

R&D Center, Blanks Division\*

HOYA Corporation

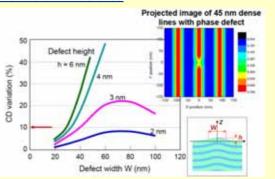

## Critical issues of EUV mask substrates

#### **CTE**

Requirement : < ± 5ppb/K in production

Low Thermal Expansion Material

(LTEM) will be needed

In HOYA, Corning ULE (SiO<sub>2</sub>-TiO<sub>2</sub> glass)

is mainly used as EUV mask substrate

#### **Flatness**

Requirement: < 50 nm P-V on both

sides (142mm sq.)

Flatness;d

Wafer

Image Placement Error(IPE)

= (d \* tan6 ° )/4 < 4.8nm (ITRS spec. @2010)

#### **Defects**

Killer defects: 70nmW x 2nmH on ML

Simulation results T. Terasawa et al. PMJ2004

# Roughness(HSFR, MSFR, Local slope, etc.) Affect on EUV light reflectivity and LER

# **EUV** mask substrates specification (SEMI P37)

|                                              | Size or area definition                | Spec.                       | units          | Current metrology<br>in HOYA |  |

|----------------------------------------------|----------------------------------------|-----------------------------|----------------|------------------------------|--|

| Coefficient<br>of thermal<br>expansion (CTE) |                                        | Class A: ±5<br>Class B: ±10 | ppb/K          |                              |  |

| Flatness<br>(Both sides)                     | 142mm sq.                              | Class A:<30<br>Class B:<50  | nm P-V         | Corning-Tropel<br>Ultra Flat |  |

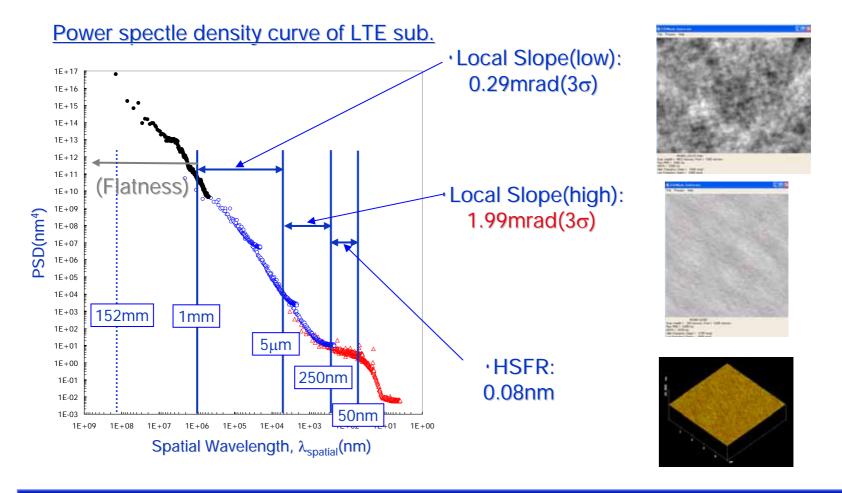

| Roughness<br>Local slope(low)                | 5μm<λ <sub>spatial</sub> <1mm          | <1.5                        | mrad<br>(3σ)   | Zygo<br>NewView              |  |

| Roughness<br>Local slope(high)               | 250nm<λ <sub>spatial</sub> <5μm        | <1.8                        | mrad<br>(3σ)   | - AFM                        |  |

| Roughness<br>HSFR                            | $50$ nm $<\lambda_{spatial}$ $<250$ nm | <0.15                       | nm-rms<br>(1σ) |                              |  |

| Defect<br>(Particle, Pit)                    | > 50nm PSL<br>equivalent size          | 0                           | counts<br>/cm² | Lasertec<br>M1350            |  |

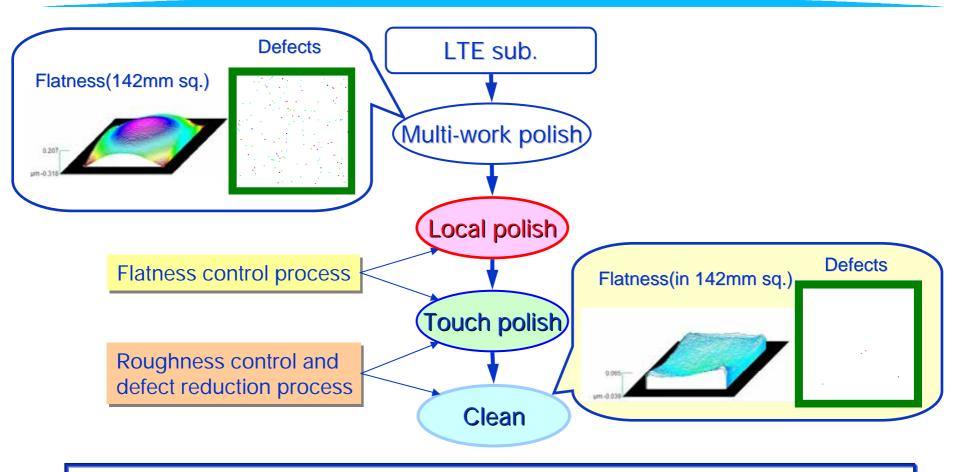

## Process flow of EUV mask substrates

Advanced processes including local polish have been developing to attain substrates with higher flatness and lower defects

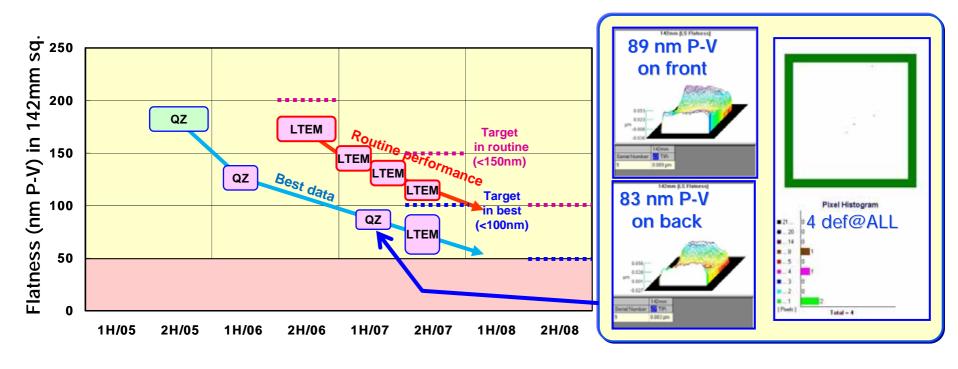

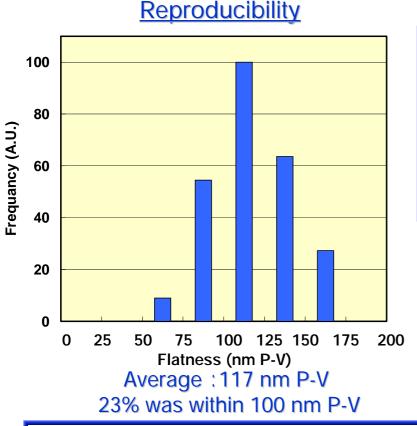

# Flatness improvement

- Substrates with high flatness and low defects can be produced using local polish

- Best flatness of ~80nm and routine flatness of ~120nm were attained in 2007

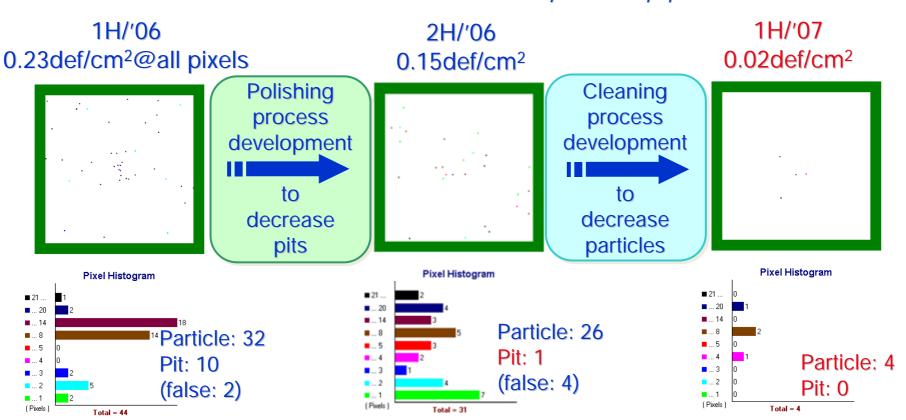

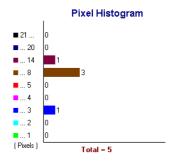

## **Defect reduction of LTE substrates**

Inspection equipment: Lasertec M1350

Defects on LTE substrates have been decreased by improvements of polishing and cleaning processes

## LTE substrates performance: Flatness and defects

Routine Target in 2007: <150 nm P-V in 142mm sq.

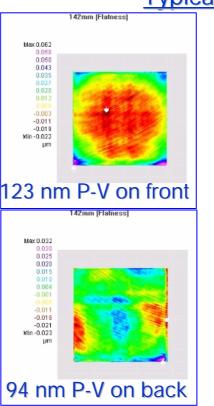

#### Typical ULE substrate

5 defects@all

LTE substrates with high flatness of 100 nm and low defects were achieved

## LTE substrates performance: Roughness

## Performance of ML blanks with LTE sub.

#### ML blank defects

20

10

13.0

13.2

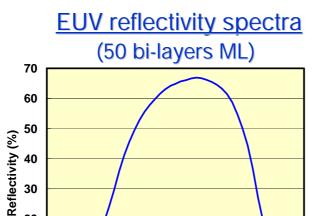

**EUV** reflectivity was measured by reflectometer located at Selete

| 13.4 13.6 13.8 14.0 |                           | Blanks        | Target  | Target  |

|---------------------|---------------------------|---------------|---------|---------|

| Wavelength (nm)     |                           | on LTEM       | in 2007 | in 2010 |

|                     | Reflectivity<br>(Peak, %) | 66.4          | >64     | >66     |

|                     | Defects on ML             | 0.13          | 0.40    | 0.20    |

|                     | (counts/cm <sup>2</sup> ) | <b>@70</b> nm | @70nm   | @40nm   |

ML blanks meeting the target spec. in 2007 can be produced by using improved ULE substrates

# **Summary**

- HOYA has been focusing on development of fabrication process for LTE substrates to attain high flatness, smooth surface and low defects, since 2006

- LTE substrates with high flatness of less than 120 nm and low defects of less than 0.05 def/cm<sup>2</sup>@60 nm can be produced by improvement of fabrication process

- We are supplying EUV blanks with LTE substrates meeting target specifications for alpha EUV exposure test

• We are now challenging further defect reduction and further flatness improvement of LTE substrates toward production target